[TI官方]US2.0电路板设计及布线指南摘录

以下内容摘自TI《US2.0电路板设计及布线指南》,文件号:zhca059a。

1.当设计一个 USB 电路板时, 最关注的信号是:

• 器件接口信号: 运行在印刷电路板 (PCB) 上的器件之间的时钟和其它信号/数据线路

• 线缆输入/输出供电: USB 连接器插槽引 脚 1(VBUS) 可能被严重滤波, 仅可通过低于大约 100KHz的低频信号。 USB 插槽的引 脚 4(模拟接地) 必须能够返还数据传输期间的电流, 且必须进行基本的滤波。

• 通过线缆, DP 及 DM 输出的差分双铰线对信号: 根据数据传输率的不同, 这些器件端子可给出具有240MHz(高速) , 6MHz(全速) , 750kHz(低速) 基频的信号。

• 外部晶振电路(器件端子 X1 和 X0) : 12MHz, 19.2MHz, 24MHz 和 48MHz 基频。 当使用一个外部晶振作为基准时钟时, 强烈推荐使用一个 24MHz 和更高频率的晶振。

2. 一般走线和安置

当为 USB 物理层 (PHY) 安排一个全新设计时, 使用以下的走线和安置指导原则。 此类指导原则有助于大大减少 4 层或更多层级评估板 (EVM) 上的信号品质及电磁干扰 (EMI) 问题。

• 首先将 USB PHY 和主要组件放置在未走线电路板上。

• 用最小的迹线长度传送高速时钟和高速 USB 差分信号。

• 只要条件允许, 在最接近接地层的层上传送高速 USB 信号。

• 使用最少的导孔和拐角传递高速 USB 信号。 这减少了信号反射和阻抗变化。

• 当不得不采取 90°弯折走线时, 以两个 45°弯折或圆弧形的走线替代单个 90°的弯折。 以通过大大减少阻抗不连续性来减少信号迹线上反射。

• 不要将 USB 迹线布置在晶振、 振荡器、 时钟信号发生器、 开关稳压器、 安装孔、 磁性器件或使用、 复制时钟信号的集成电路 (IC) 以下或靠近这些器件。

• 避免因高速 USB 信号上的残桩而引 起信号的反射。 如果残桩无法避免, 则残桩应短于 200mil。

• 通过连续层( VCC或 GND) 实现无断高速 USB 信号迹线。 避免层分割中常见的交叉分隔覆铜问题。

3.时钟走线

为了解决器件间时钟辐射的问题, 请将一个大约为 10 至 130Ω 的电阻器与时钟信号串联。 采用试错法, 在高速示波器上查看时钟波形的形状, 并调节电阻值, 以大大减少波形失真。 此电阻值应尽可能的小以实现预期效果。 电阻应靠近生成时钟信号的器件。 如果采用了外部晶振, 则应遵循《德州仪器 (TI) USB 2.0 器件所用晶振的选择和技术规格》 (SLLA122) 中详述的指导原则。

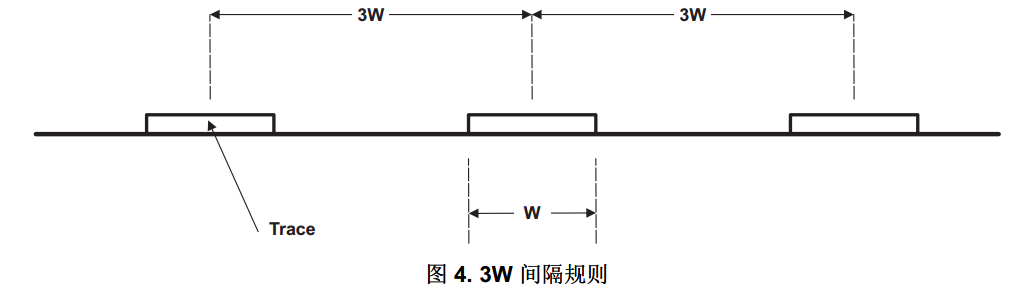

当进行器件间时钟迹线的布线时, 可尝试使用3 W 间隔规则。 时钟迹线的中心至任意邻近信号迹线中心的距离应至少为时钟迹线宽度的 3 倍。 许多时钟, 其中包括低频时钟, 可具有很快的上升和下降时间。 采用3W 规则可削减迹线间的串扰。 一般来说, 器件间并行的走线之间也应当保持一定 的空间。 避免采用直角来布置走线, 以大大减少走线长度及阻抗的不连续性。 要进一步保护器件不受串扰影响, 尽可能地在时钟信号线旁侧布置保护迹线(GND 引 脚至 GND 引 脚)。 如图 4所示, 这样可减少时钟信号耦合

4.DP/DM 迹线

USB PHY 应尽可能的接近 USB 2.0 连接器。 高速运转期间, DP/DM 线路上的信号摆幅相对较小 (400mV± 10%), 因此双绞线所拾取的任意差分噪音都会影响接收到的信号。 当 DP/DM 迹线不具有任何屏蔽措施时, 迹线的运行方式往往像一条天线, 有可能拾取环境中周围元件所产生的噪声。 为了尽可能的降低这个运行方式的影响:

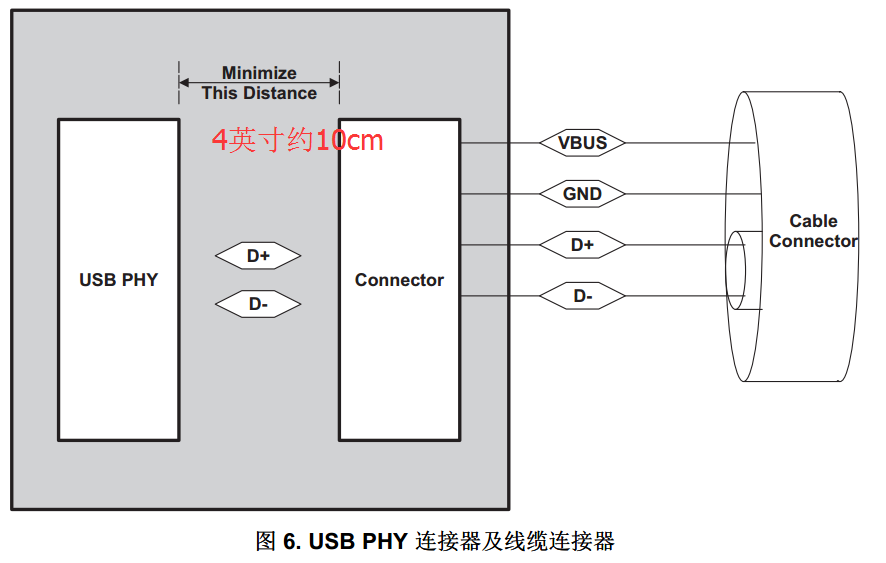

• DP/DM 迹线应始终保持长度匹配, 并且须保持在 4 英寸的长度内; 否则, 信号眼图的开眼范围将降低(请参见图 6) 。

• DP/DM 的走线应尽可能相互接近以实现差分信号的噪声抑制, 迹线采取并联, 间距不超过 2mil(以芯片封装边界为测量起始点, 而非焊球或引 脚)。

• 高速 USB 连接通过屏蔽双绞线对实现, 此双绞线具有 90Ω ± 15% 的差分特性阻抗。 在布线时, DP 及DM 的阻抗均应为 45Ω ± 10%。

• DP/DM 迹线不应具有任一额外组件无法以保持信号完整性。 例如, 迹线不能路由经过两个 USB 连接器。

5.模拟、 锁相环 (PLL) 和数字电源滤波

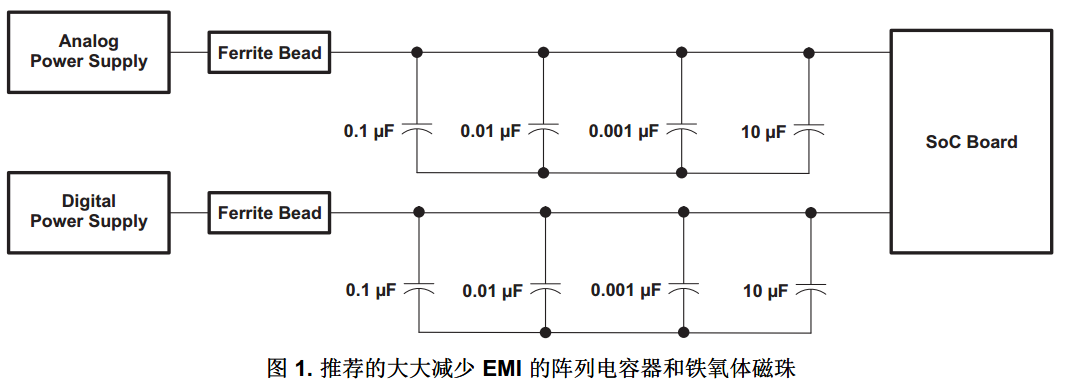

为了大大减少 EMI 辐射, 在模拟、 锁相环 (PLL) 和芯片数字部分的电源端子上添加具有铁氧体磁珠的去耦合电容器。 将这个阵列放置在尽可能靠近芯片的位置来大大减少线路的电感以及系统内的噪声。 图 1 中显示了一个模拟和数字电源示例。 在具有同样功能的多个电源引 脚的情况下, 将它们一起接至电路板上的一个单个低阻抗点上, 然后除了铁氧体磁珠以外, 添加去耦合电容器。 这个电容器和磁珠阵列改进了 EMI 和滤波性能。 在更改配置前, 请将 EMI 和抖动考虑在内。

凯特网版权声明:以上内容允许转载,但请注明出处,谢谢!